Q518D

## **Features**

- Component level MDA test and circuit level ATE test can do in the same platform at the same time to save the man hour in test station.

- Cost effective :integrated MDA module and function module at any time you want to realize your complicated test work.

- Both MDA and ATE automatic switch, additional fixture isolation does not require.

- Security :your already exist function module can integrated as a partial of this system through software or hardware linking. You need not to tell us the detail technique about you products.

- Flexibility: you can bundle any test module from current system easily upon you products innovation. You can update your system just in time.

- Nature graphic simulation interface, so that you can debug your test program very easily.

- Oracle Data base architecture, users can program their special facilities/functions by their own without modify the system software.

# **Function:**

- 1.Data base architecture, the test results data write to data base to realize central data acquisition, analysis, remote monitoring facilities.

- 2. Supply a DC constant voltage constant current from a programmable power supply (PPS) to DUT to protect the damage through the test.

- 3.Supply AC220V/110V AC from AC source, voltage, frequency and trip protect is essential.

- 4.Dynamic test: test the voltage, current, waveform, frequency at the test point you assigned, and simulation the test activities through dry contact relay to realize the fully automatic test.

- 5. Support 14sets per card 0.5ms 1 Amp high speed dry contact relay card, maximum 42 sets contact relay to realize the manipulation of the test.

- 6.Support 10 sets per card maximum 30 sets 16A/250V high current dry relay contact facility to explain the additional power module for this system.

- 7.Flexible architecture: combine 3/6/11 wires measurement, you can choose the best solution for your test need

- 8.Digital input function:32 channels per switch card, maximum 256 channels digital input to monitoring the test data on the DUT.

### Console:

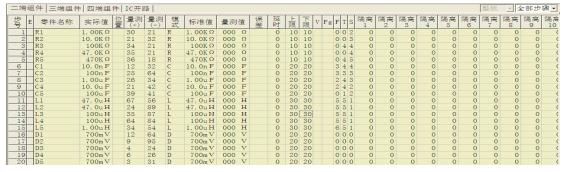

### 1. Edit screen

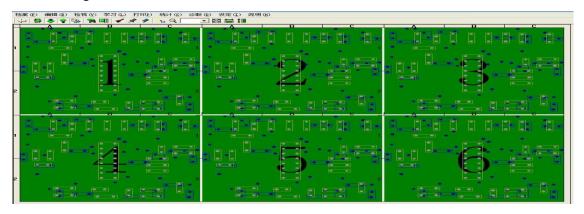

### 2. Plate diagram

| Device configuration                                                      |                                                  |                                                                                                               |                 |                    |      |                                                 |  |

|---------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|--------------------|------|-------------------------------------------------|--|

| Test points                                                               |                                                  | Standard<br>Configuration                                                                                     | 256<br>Channels | Maximu<br>m Points | 1024 | Maximum Expanded Charge Points 65536 Customized |  |

| Channel<br>board                                                          | CMOS<br>+Relay                                   | 128 channels per channel board                                                                                |                 |                    |      |                                                 |  |

| Isolation points                                                          |                                                  | 10 per test step, automatic learning isolation                                                                |                 |                    |      |                                                 |  |

| Source                                                                    | Conventional<br>signal<br>Source                 | DCV:±10mV~±7.5V OR 15V ACV:10mVpp~10Vpp ACDVI:10u~20mA                                                        |                 |                    |      |                                                 |  |

|                                                                           | Test<br>frequency                                | 100、1000、10K、100KHz、2MHz、(50Hz)                                                                               |                 |                    |      |                                                 |  |

| Test step                                                                 |                                                  | No limit                                                                                                      |                 |                    |      |                                                 |  |

| Test frequency                                                            |                                                  | component test: 1ms~40ms O/S test: 05 s /102                                                                  |                 |                    |      |                                                 |  |

| Test<br>scope                                                             | Resistance                                       | $0.052\sim100$ M $\Omega$ (2-wire type) 1% $\sim$ 5% (4-wire type) 10m $\Omega$                               |                 |                    |      |                                                 |  |

|                                                                           | Capacitance                                      | 1pF~40mF±2%~5%                                                                                                |                 |                    |      |                                                 |  |

|                                                                           | Inductance                                       | 1uH~50H±2%~5%                                                                                                 |                 |                    |      |                                                 |  |

|                                                                           | Diode                                            | 0.1~9V±1%~3%                                                                                                  |                 |                    |      |                                                 |  |

|                                                                           | Zener diode                                      | 0.1~15V±1%~3%                                                                                                 |                 |                    |      |                                                 |  |

|                                                                           | Transistor                                       | Vce saturation voltage and B value are tested in three stages                                                 |                 |                    |      |                                                 |  |

|                                                                           | field-effect<br>transistor                       | Vds.Cds&Rd (on)                                                                                               |                 |                    |      |                                                 |  |

|                                                                           | Optical<br>coupler and<br>power failure<br>organ | The four terminals test their on-voltage or resistance                                                        |                 |                    |      |                                                 |  |

| Impedance series-parallel connection                                      |                                                  | Using multi-frequency test and phase separation method (8 ~82 degrees)                                        |                 |                    |      |                                                 |  |

| Polarity of Electrolytic<br>Capacitor and Leakage<br>Detection Technology |                                                  | Three-terminal characteristic discrimination comparison technology test and two-terminal leakage current test |                 |                    |      |                                                 |  |

| Feature<br>selection<br>function                                          | Microresistor<br>(4-wire<br>Type)                | Minimum 50mQ (4-wire) ± 10mΩ                                                                                  |                 |                    |      |                                                 |  |

|                                        | DRMode                              | Detectable diode or IC forward parallel leakage and empty soldering                                                              |  |

|----------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

|                                        | Key press                           | During the key test, the program is suspended, and manual operation is used                                                      |  |

|                                        | function                            | to detect whether the key is good or bad                                                                                         |  |

|                                        | Automatic<br>stamp                  | Test PASS or Fail automatic stamping equipment                                                                                   |  |

|                                        | Monitor placement                   | Monitoring placement orientation (PASS or Fail shunt)                                                                            |  |

|                                        | Multi-<br>pressure bed              | Multi-or double-press system                                                                                                     |  |

|                                        | First pass<br>yield<br>surveillance | When the first pass yield < X% is the alarm bell and < Y% is the alarm bell, stop the line inspection                            |  |

|                                        | Graphic function                    | Board View)& Automatic Production of Board View                                                                                  |  |

|                                        | Connecting<br>board<br>function     | The linking board is automatically unfolded & the sub-board is selected and tested & the linking board is automatically detected |  |

|                                        | Test data archiving                 | Save the test data selection items & barcode scanning                                                                            |  |

|                                        | SFIS                                | ShineWave SFIS、Sajet SFIS、Off-Line SFIS                                                                                          |  |

|                                        | re protection nction                | Infrared protection function                                                                                                     |  |

| Operating system                       |                                     | Windows XP                                                                                                                       |  |

| Computer configuration                 |                                     | CPU: Dual Core 2.8+Memory: 2GB/ Hard Disk: 1000G+G/Monitor: 19 "Monitor                                                          |  |

| Printer                                |                                     | Epson Bill printer                                                                                                               |  |

| Machine size (length * width * height) |                                     | 1000mm*750mm*1600MM (Machine size can be customized according to customer requirements)                                          |  |

| Circuit board dimensions               |                                     | 500mmX350mm                                                                                                                      |  |

| Air pressure demand                    |                                     | 3~6Kgs/cm2                                                                                                                       |  |

| Working Environment-<br>Power Supply   |                                     | Temperature 0-45 degrees, humidity 10-90%&AC220V                                                                                 |  |